# DESIGN OF EFFICIENT SHIFT REGISTERS USING PULSED LATCHES

<sup>1</sup>M. Ajay, <sup>2</sup>G.Srihari,

<sup>1</sup>PG Scholar, Dept of ECE, Sreenivasa Institute of Technology and Management Studies (Autonomous) Murkambattu, Chittoor, JNTU Anatapur University

<sup>2</sup>Assistant Professor, Dept of ECE, Sreenivasa Institute of Technology and Management Studies (Autonomous) Murkambattu, Chittoor JNTU Anatapur University.

#### Abstract:

This paper proposes a low-power and area-efficient shift register using digital pulsed latches. The area and power consumption are reduced by replacing flip-flops with pulsed latches. This method solves the timing problem between pulsed latches through the use of multiple non-overlap delayed pulsed clock signals instead of the conventional single pulsed clock signal. The shift register uses a small number of the pulsed clock signals by grouping the latches to several sub shifter registers and using additional temporary storage latches. A 256-bit shift register using pulsed latches was fabricated using a  $0.18\mu$ m CMOS process with VDD = 1.8V. The core area is  $6600\mu$ m2. The power consumption is 1.2mW at a 100 MHz clock frequency.

Keywords: Area-efficient, flip-flop, pulsed clock, pulsed latch, shift register.

## 1. INTRODUCTION

Flip flops are the basic storage elements used extensively in all kinds of digital designs. As the feature size of CMOS technology process scaled down according to Moore's Law, designers are able to integrate many numbers of transistors onto the same die. Heat is one of the phenomenon packaging challenges in this epoch, it is one of the main challenges of low power design methodologies and practices. Another driver of low power research is the reliability of the integrated circuit. More switching implies higher average current is expelled and therefore the probability of reliability issues occurring rises. We are moving from laptops to tablets and even smaller computing digital systems. With this profound trend continuing and without a match trending in battery life expectancy, the more low power issues will have to be addressed. The current trends will eventually mandate low power design automation on a very large scale to match the trends of power consumption of today's and future integrated chips. Power] consumption of Very Large Scale Integrated design is given by Generalized relation, P = CV2f[1].

Since power is proportional to the square of the voltage as per the relation, voltage scaling is the most prominent way to reduce power dissipation. However, voltage scaling is results in threshold voltage scaling which bows to the exponential increase in leakage power. Though several contributions have been made to the art of single edge triggered flip-flops, a need evidently occurs for a design that further improves the performance of single edge triggered flipflops patterns. The architecture of a shift register is quite simple. An N-bit shift register is composed of series connected N data flip-flops. The speed of the flipflop is less important than the area and power consumption because there is no circuit between flip-flips in the shift register. The smallest flip-flop is suitable for the shiftregister to reduce the area and power consumption.

### 2. SHIFT REGISTERS

A shift register is the basic building block in a VLSI circuit. Shift registers are commonly used in many applications, such as digital filters, communication receivers and image processing ICs Recently, as the size of the image data continues to increase due to the high demand for high quality image data, the word length of the shifter register increases to process large image data in image processing ICs. An image-extraction and vector generation VLSI chip uses a 4K-bit shift register A 10-bit 208 channel output LCD column driver IC uses a 2K-bit shift register A 16- megapixel CMOS image sensor uses a 45K-bit shift register. As the word length of the shifter register increases, the area and power consumption of the shift register to reduce the area and power consumption. Recently, pulsed latches have replaced flipflops in many applications, because a pulsed latch is much smaller than a flip-flop. But the pulsed latch cannot be used in a shift register due to the timing problem between pulsed latches.

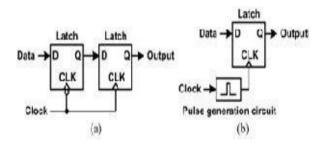

Fig.1. (a) Master slave flip flop (b) Pulsed latch

There are also 'bidirectional' shift registers which allow shifting in both directions:  $L \rightarrow R$  or  $R \rightarrow L$ . The serial input and last output of a shift register can also be connected to shift register' Previous work often measured energy consumption using a limited set of data patterns with the clock switching every cycle. But real designs have a wide variation in clock and data activity across different TE instances. For example, lowpower microprocessors make extensive use of clock gating resulting in many TEs whose energy consumption is dominated by input data transitions rather than clock transitions.

## **3. PROPOSED ARCHITECTURE**

#### INTERNATIONAL RESEARCH JOURNAL IN ADVANCED ENGINEERING AND TECHNOLOGY (IRJAET) E - ISSN: 2454-4752 P - ISSN : 2454-4744 VOL 2 ISSUE 3 (2016) PAGES 1100 - 1106 RECEIVED : 05/06/2016. PUBLISHED : 21/06/2016

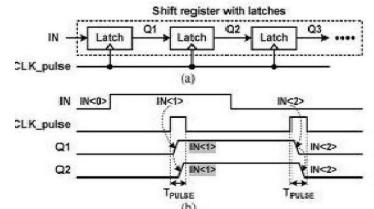

The pulsed latch cannot be used in shift registers due to the timing problem, as shown in Fig. 2. The shift registers in Fig. 2(a) consists of several latches and a pulsed clock signal (CLK\_pulse). The operation waveforms in Fig. 2(b) show the timing problem in the shifter register. The output signal of the first latch (Q1) changes correctly because the input signals of the first latch (IN) is constant during the clock pulse width (TPULSE). But the second latch has an uncertain output signal (Q2) because its input signal (Q1) changes during the clock pulse width. One solution for the timing problem is to add delay circuits between

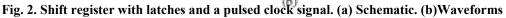

Fig. 3. Shift register with latches, delay circuits, and a pulsed clock signal. (a)Schematic. (b)Waveforms

latche. The output signal of the latch is delayed and reaches the next latch after the clock pulse. the output signals of the first and second latches (Q1 and Q2) change during the clock pulse width , but the input signals of the second and third latches (D2 and D3) become the same as the output signals of the first and second latches (Q1 and Q2) after the clock pulse. As a result, all latches have constant

#### INTERNATIONAL RESEARCH JOURNAL IN ADVANCED ENGINEERING AND TECHNOLOGY (IRJAET) E - ISSN: 2454-4752 P - ISSN : 2454-4744 VOL 2 ISSUE 3 (2016) PAGES 1100 - 1106 RECEIVED : 05/06/2016. PUBLISHED : 21/06/2016

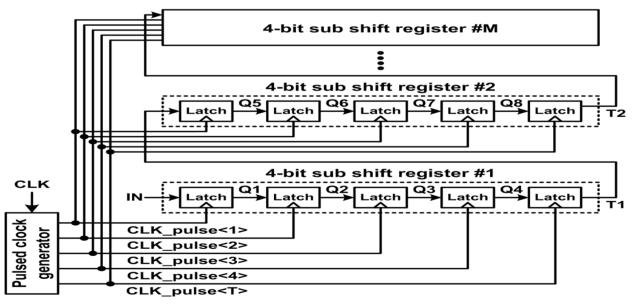

input signals during the clock pulse and no timing problem occurs between the latches. However, the delay circuits cause large area and power over heads. The proposed shift register is divided into M sub shifter registers to reduce the number of delayed pulsed clock signals. A 4-bitsub shifter register consists of five latches and it performs shift operations with five non-overlap delayed pulsed clock signals(CLK\_pulse1:4 and CLK \_pulseT). In the 4-bit sub shift register #1, four latches store 4-bit data (Q1-Q4) and the last latch stores 1-bit temporary data (T1) which will be stored in the first latch (Q5) of the 4-bit sub shift register #2.

# 4. **RESULTS**

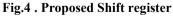

Fig:5. 32 Bit Shift Register using SSASPL

| Nerilog File                                                                                            | ×                        |

|---------------------------------------------------------------------------------------------------------|--------------------------|

| V DSCH 2.7f                                                                                             | Size Labela              |

| // 4/22/2016 8:26:11 AM                                                                                 | Routing startegy         |

| // G:\projects\my project\DL-PG-32bitfigure.sch                                                         | Metal 1.2.3              |

|                                                                                                         | Metal 1,2,3              |

| module DL-PG-32bitfigure( clk2,in1,CO_2,CO_T,CO_1,o_T7,o_T5,o<br>o T3.o T1.o T2.CO 3.CO 4.Q.o T6.out14. | Add Vertical bus         |

| 0_13,0_11,0_12,00_3,00_4,0,0_16,00114,<br>out15):                                                       | Add ventical bus         |

| input clk2.in1:                                                                                         |                          |

| output CO 2,CO T,CO 1,o T7,o T5,o T4,o T3,o T1;                                                         | I/O Floorplan            |

| output o_T2,CO_3,CO_4,Q,o_T6,out14,out15;                                                               | Free placement           |

| wire w117,w118,w119,w120,w121,w122,w123,w124;                                                           | Fixed I/Os (IBIS) Loac   |

| <b>v</b>                                                                                                | T I Ked I/OS (IDIS)Edac  |

| < ►                                                                                                     | Limit row width to       |

|                                                                                                         |                          |

| 260. Routed 1 wires "w85"                                                                               | 2000 µm                  |

| 250. Routed 1 wires "w86"                                                                               |                          |

| 240. Routed 3 wires "w65"                                                                               | Compiler Status          |

| 230. Routed 3 wires "o_T6"<br># Scan Clocks and Pwl                                                     | Compiled cells : 245/245 |

| # Scan Clocks and Pwi<br># Clock clk2, period 1.00ns                                                    |                          |

| # Clock in1, period 2.00ns                                                                              | Routed wires : 151       |

| Lavout width=2021um, height=323um                                                                       | Pads:0                   |

| (Compiler End - No error)(8:28:09 AM)                                                                   | No error                 |

| · · · · · · · · · · · · · · · · · · ·                                                                   | No eno                   |

|                                                                                                         |                          |

|                                                                                                         |                          |

| 📴 Compile 🛛 🗰 Show grid 🛛 🖌 Back to editor 🛛 off                                                        | 🧼 Help 🚽                 |

|                                                                                                         |                          |

| 121                                                                                                     | <b>F</b> ///             |

Fig:6 Area of the 32 Bit Shift Register using SSASPL

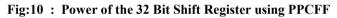

The proposed shift register using pulsed latches were implemented with the 32 and 16 bit SSASPLs achieves a small area and low power consumption compared to the 32 and 16 bit PPCFF.

#### INTERNATIONAL RESEARCH JOURNAL IN ADVANCED ENGINEERING AND TECHNOLOGY (IRJAET) E - ISSN: 2454-4752 P - ISSN : 2454-4744 VOL 2 ISSUE 3 (2016) PAGES 1100 - 1106 RECEIVED : 05/06/2016. PUBLISHED : 21/06/2016

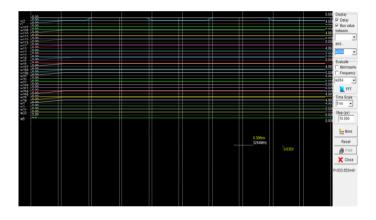

Fig:7 Power of the 32 Bit Shift Register using SSASPL

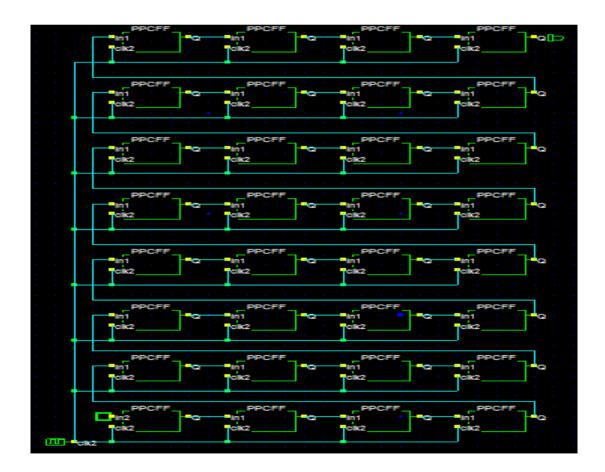

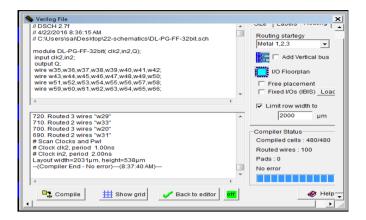

Fig:8. 32 Bit Shift Register using PPCFF

# **COMPARISION ANALYSIS**

| PARAMETERS | PPCFF                 | SSASPL         |

|------------|-----------------------|----------------|

| 1. Area    | $31.41 \mu m^2$       | $8.42 \mu m^2$ |

| 2. Power   | 6.611 <sup>[mW]</sup> | 2.876<br>[mW]  |

Table:1 Comparision of Area and Power of SSASPL and PPCFF

| PARAMETERS | PPCFF                    | SSASPL               |

|------------|--------------------------|----------------------|

| 1. Area    | 60.25<br>μm <sup>2</sup> | 33.63µm <sup>2</sup> |

| 2. Power   | 244.92<br>[mW]           | 381.39<br>[mW]       |

Table:2 Comparision of Area and Power of 16 bit Shift Register using SSASPL and PPCFF

June 21, 2016

|            | PPCFF     | SSASPL    |

|------------|-----------|-----------|

| PARAMETERS |           |           |

| 1. Area    | 90.926    | 6.527     |

|            | $\mu m^2$ | $\mu m^2$ |

| 2. Power   | 533.55    | 313.61    |

|            | [mW]      | [mW]      |

Table:3 Comparision of Area and Power of 32 bit Shift Register using SSASPL and PPCFF

# CONCLUSION

This paper proposed a low-power and area-efficient shift register using pulsed latches. The shift register reduces area and power consumption by substituting flip-flops with pulsed latches. The timing problem between pulsed latches is solved using multiple non-overlap delayed pulsed clock signals as an alternative of a single pulsed clock signal.

## REFERENCES

[1] Xiaowen Wang, and William H. Robinson, "A Low-Power Double Edge Triggered Flip-Flop with TransmissionGates and Clock Gating" IEEE Conference, pp 205-208, 2010.

[2] PhaedonAvouris, JoergAppenzeller, Richard Martel, and Shalom J. Wind. "Carbon nanotubeelectronics".Proceedings of the IEEE,91(11):1772–84, November 2003.

[3] Fabien Pregaldinyet.al., "Design Oriented Compact Models for CNTFETs", IEEE Trans. Elec. dev., 2006.

[4] -Flop Based on Signal Feed-Through Scheme"International Journal of Advanced Research inElectronics and Communication Engineering(IJARECE) Volume 3, Issue 11, November 2014.

[5] S. Heo, R. Krashinsky, and K. Asanovic, "Activity-sensitive flip-flopand latch selection for reduced energy," IEEE Trans. Very Large ScaleIntegr. (VLSI) Syst., vol. 15, no. 9, pp. 1060–1064, Sep. 2007.