# ENERGY EFFICIENT FREQUENCY MULTIPLIER FOR SYSTEM ON CHIP

<sup>1</sup>D.Sangeetha, <sup>2</sup>A.Karthika,

<sup>1</sup>PG Scholar, Dept Of ECE, Excel College Of Engineering And Technology, <sup>2</sup>Assistant Professor, Dept Of ECE, Excel College Of Engineering And Technology.

#### ABSTRACT

A logic gate-based digital frequency multiplication technique for low-power frequency synthesis is presented. The proposed digital edge combining approach offers broadband operation with low- power and low- area advantages and is a promising candidate for low- power frequency synthesis in deep submicrometer CMOS technologies. Chip prototype of the proposed frequency multiplication-based 2.4-GHz binary frequency-shift- keying (BFSK)/amplitude shift keying (ASK) transmitter (TX) was fabricated in 0.13-µm CMOS technology. The TX achieves maximum data rates for BFSK and ASK modulations, respectively, consuming The corresponding energy efficiencies for BFSK for ASK modulations.

**Keywords:** Binary frequency-shift-keying (BFSK) transmitter (TX), class-D power amplifier (PA), energy efficient, frequency multiplication technique.

#### 1. INTRODUCTION

Low-power and low-area transmitter (TX) architectures are essen- tial for short-range communications such as wireless sensor networks, body area networks, and other battery operated applications. These low-power applications have relaxed requirements on phase noise, spectral purity, and

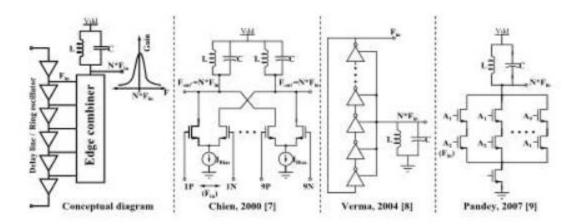

#### **Fig.1.** Frequency multiplication circuit techniques

other performance metrics of TX, which can be used as an extra degree of freedom in the TX architecture

April 04, 2017

design. Phase-locked loop (PLL)-based TXs are both power and area efficient compared with the conventional mixer-based direct up-conversion TX architectures. The power consumption in frequency synthesis can be minimized by operating the PLL at lower frequencies and using frequency multiplier circuits outside the loop to generate the up-converted RF carrier The power consumption in frequency synthesis can be minimized by operating the PLL at lower frequencies and using frequency multiplier circuits outside the loop to generate the up- converted RF carrier, Open-loop PLL-based TX achieves high data rates, but its trans- mission quality is affected by the increased close-in phase noise of voltagecontrolled oscillator (VCO), frequency drift due to pressure, volume, and temperature (PVT) variations and disturbances in VCO control line during modulation, and other nonideal effects. In this brief, we exploit the higher transition frequency (90 GHz, 130 nm) and improved matching performance (for the same device area, W\*L) [11] offered by the deep sub micrometer devices and demonstrate a static logic gate-based frequency multiplier design for low-power frequency synthesis. The presented digital edge combiner (EC) offers broadband operation with rail-to-rail output swing, low-power, and low-area implementation advantages. The power and area advantages of the proposed digital frequency mul-tiplier comes with a tradeoff in the spectral purity of the generated RF carrier, which is acceptable in the lowpower and short-range wireless communication standards.

### 2. FREQUENCY MULTIPLICATION

The block diagram of frequency multiplication-based binary frequency-shift-keying (BFSK)/amplitude shift keying a small area penalty. As only one PD-N is added to each differential output of the edge combiner when the maximum multiplication ratio is increased by one, the output loading of the edge combiner increases slower than that of the edge combiner in . However, the PD-N should remain on till the positive and the negative edges of the multiplied differential clocks are generated by the edge combiner. In addition, when the PD-N is turned ON, the edge combiner uses a small-sized PU-P to prevent conflict between the PU-P and the PD-N. Because of these restrictions, the frequency multiplier in may not be suitable for high-speed operation and cannot guarantee 50% duty cycle for the multiplied clock. Finally, interphase timing distortion may occur when the multiphase clocks pass through the multiplication-ratio control logic, which in turn can generate pulse, suitable for high-frequency multiplied clock generation with low power and a small area. It can also guarantee a 50% duty cycle for its multiplied clock. However, because the output pulses of the pulse generator are generated consecutively [i.e., the kth pulse is generated directly following the (k-1)th pulse], the pulses might overlap owing to process variation or layout mismatch as they pass through the multiplication-ratio control logic; this could cause a short-circuit current to flow in the edge combiner, which in turn could lead to excessive power consumption or malfunction of the frequency multiplier. In addition, the output loading of the edge combiner rapidly increases with the multiplication ratio.

### 3. PROPOSED SYSTEM

To enhance the lock time, which is an important design parameter in the clock generator, a dualedge-triggered phase-detector-based DLL core is adopted. Similar to pre- vious frequency multipliers, the proposed frequency multiplier is also composed of a pulse generator, a multiplication-ratio control logic, and an edge combiner. ratio control signal. Finally, the high-speed and highly reliable edge combiner INTERNATIONAL RESEARCH JOURNAL IN ADVANCED ENGINEERING AND TECHNOLOGY (IRJAET) E - ISSN: 2454-4752 P - ISSN : 2454-4744 VOL 3 ISSUE 2 (2017) PAGES 1988 – 1992 RECEIVED: 15-03-2017. PUBLISHED: 04-04-2017.

April 04, 2017

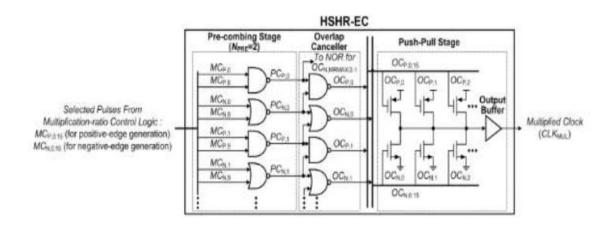

#### **Fig.2.Proposed Structure**

(HSHR-EC) generates one multiplied clock (CLKMUL) using all the outputs of the multiplication- ratio control logic. Since the number of multiphase is 32, the maximum multiplication ratio is 16. HSHR-EC. As the number of signals merged in the pre combining stage (NPRE) increases, the number of PU-Ps and PD-Ns required in the push–pull stage are reduced by a factor of NPRE. It might appear that, by increasing NPRE, the maximum multiplied clock frequency of the HSHR-EC can be enhanced; however, because the logic depth and the number of NAND and NOR gates in the pre combing stage are equal to log2NPRE and 32(1–1/NPRE.

# 4. RESULT ANALYSIS

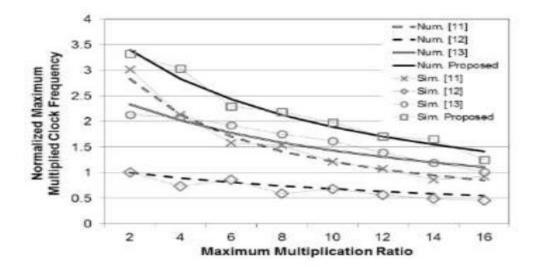

Fig.3. Numerical analysis and simulation results

April 04, 2017

The maximum multiplied clock frequency of the proposed frequency multiplier is compared with the previous frequency multipliers. Because it is determined by the edge-combiner structure, he normalized channel widths of the PU-P and the output buffer with respect to the channel width of the PD-N, fMUL,MAX is the maximum multiplied clock frequency, and ERRDUTY is the duty-cycle error of the multiplied clock. However, because the precombining stage in the HSHR-EC merges two signals into one, the self-loading of the push–pull stage (output loading of the push–pull stage except the loading

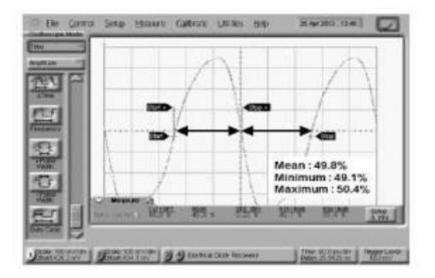

Fig.4. Measured waveform of the multiplied clock

induced by the output buffer) is halved. The frequency multiplier in has the best performance among the previous frequency multipliers, because the modified DCVSL stage in its edge combiner has better features than that of the edge combiners require a high operating frequency. Thus, the proposed clock generator (frequency multiplier with DLL core) achieves the lowest power consumption to frequency ratio among the DLL with frequency multiplier architectures. Because the proposed clock generator has the highest maximum multiplication ratio and the areas of the DLL core and the frequency multiplier are proportional to the maximum multiplication ratio, the area of the proposed clock generator is larger than that of previous DLL with frequency multiplier architectures. However, the normalized area of the proposed clock generator, which is the area divided by the product of the square of the process technology and the maximum multiplication ratio, is lower than that of other clock generators. where MRMAX is the maximum multiplication factor. Compared with DLL with frequency multiplier architectures, the proposed clock generator shows the superior performance according to both FoM1 and FoM2, as expected. Note that both the multiplying DLL and the PLL architecture in [18] show superior performance than the proposed clock generator in FoM1. Even the area and the multiplication ratio are consid- ered using FoM2, the multiplying DLL in is still shows better performance than the proposed clock generator. This result is mainly due to the outstanding power consumption of the multiplying DLL and the PLL architecture.

## CONCLUSION

In this paper, a frequency multiplier for a DLL-based clock generator is proposed. The proposed HSHC-EC guarantees high-speed operation owing to its hierarchical edge-combiner structure and highly reliable operation owing to its use of an overlap canceller. The optimized pulse generator and the multiplication-ratio control logic are proposed to reduce the delay difference between positive and negative edge generation paths. Finally, a numerical analysis is performed to validate its performance.

### REFERENCES

[1] T. D. Burd, T. A. Pering, A. J. Stratakos, and R. W. Brodersen, "A dynamic voltage scaled microprocessor system," IEEE J. Solid-State Circuits, vol. 35, no. 11, pp. 1571–1580, Nov. 2000.

[2] Z. Cao, B. Foo, L. He, and M. van der Schaar, "Optimality and improvement of dynamic voltage scaling algorithms for multimedia applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 3, pp. 681–690, Mar. 2010.

[3] M. Elgebaly and M. Sachdev, "Variation-aware adaptive voltage scaling system," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 5, pp. 560–571, May 2007.

[4] C. Kim, I. C. Hwang, and S.-M. Kang, "A low-power small-area ±7.28-ps-jitter 1-GHz DLL- based clock generator," IEEE J. Solid-State Circuits, vol. 37, no. 11, pp. 1414–1420, Nov. 2002.

[5] G. Chien and P. R. Gray, "A 900-MHz local oscillator using a DLL-based frequency multiplier technique for PCS applications," IEEE J. Solid-State Circuits, vol. 35, no. 12, pp. 1996–1999, Dec. 2000.

[6] T.-C. Lee and K.-J. Hsiao, "The design and analysis of a DLL-based frequency synthesizer for UWB application," IEEE J. Solid-State Circuits, vol. 41, no. 6, pp. 1245–1252, Jun. 2006.

[7] C.-N. Chuang and S.-I. Liu, "A 40 GHz DLL-based clock generator in 90 nm CMOS technology," in IEEE Int. Solid-State Circuit Conf. Dig. Tech. Paper, 2007, pp. 178–595.

[8] P. C. Maulik and D. A. Mercer, "A DLL-based programmable clock multiplier in 0.18-μm CMOS with -70 dBc reference spur," IEEE J. Solid-State Circuits, vol. 42, no. 8, pp. 1642–1648, Aug. 2007.